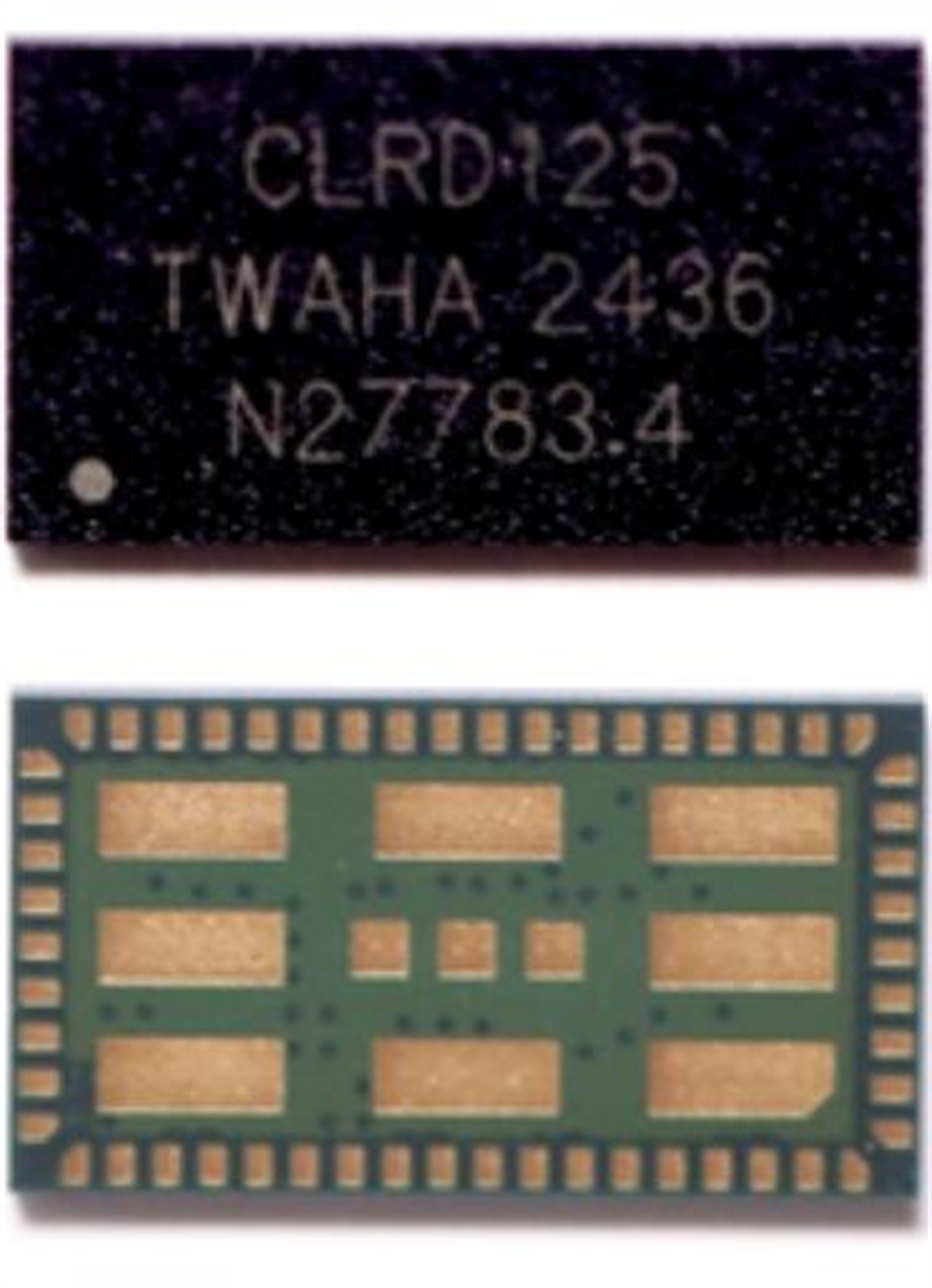

De CLRD125 ass en héichperformante, multifunktionelle Redriver-Chip, deen en Dual-Port 2:1 Multiplexer an eng 1:2 Switch/Fan-out Bufferfunktioun integréiert. Dësen Apparat ass speziell fir Héichgeschwindegkeets-Dateniwwerdroungsapplikatiounen entwéckelt ginn, ënnerstëtzt Datenraten vu bis zu 12,5 Gbps, an ass gëeegent fir verschidde Héichgeschwindegkeets-Interfaceprotokoller wéi 10GE, 10G-KR (802.3ap), Fibre Channel, PCIe, InfiniBand, an SATA3/SAS2.

De Chip huet en fortgeschrattene kontinuéierlechen Zäitlinearen Equalizer (CTLE), deen effektiv Signalverloschter iwwer grouss Distanzen, bis zu 35 Zoll FR-4-Gedréckte Leiterplat oder 8 Meter AWG-24-Kabel, mat enger Iwwerdroungsrate vun 12,5 Gbps kompenséiert, wat d'Signalintegritéit däitlech verbessert. Den Transmitter benotzt en programméierbaren Design, deen et erlaabt, d'Ausgangsschwankung flexibel am Beräich vun 600 mVp-p bis 1300 mVp-p unzepassen, an ënnerstëtzt De-Emphasis vu bis zu 12dB fir Kanalverloschter effektiv ze iwwerwannen.

Déi flexibel Konfiguratiounsméiglechkeeten vum CLRD125 erméiglechen eng nahtlos Ënnerstëtzung fir verschidde Transmissiounsprotokoller, dorënner PCIe, SAS/SATA an 10G-KR. Besonnesch am 10G-KR- a PCIe Gen3-Modi kann dëse Chip transparent Link-Trainingsprotokoller verwalten, wat Interoperabilitéit op Systemniveau garantéiert an d'Latenz miniméiert. Dës intelligent Protokolladaptabilitéit mécht de CLRD125 zu enger Schlësselkomponent an High-Speed-Signaltransmissiounssystemer a bitt den Designingenieuren e mächtegt Tool fir d'Systemleistung ze optimiséieren.

**Produkt Highlights:**

1. **12,5 Gbps Dual-Channel 2:1 Multiplexer, 1:2 Switch oder Fan-Out**

2. **Gesamtstroumverbrauch vun nëmmen 350 mW (Typesch)**

3. **Fortgeschratt Signalkonditionéierungsfeatures:**

- Ënnerstëtzt bis zu 30dB Empfangsausgläichung bei enger Linnrate vun 12,5 Gbps (Frequenz vun 6,25 GHz)

- Transmissiounsde-Emphasis-Kapazitéit vu bis zu –12dB

- Kontroll vun der Senderausgangsspannung: 600mV bis 1300mV

4. **Konfiguréierbar iwwer Chip Select, EEPROM oder SMBus Interface**

5. **Industriellen Betribstemperaturberäich: –40°C bis +85°C**

**Uwendungsberäicher:**

- 10GE

- 10G-KR

- PCIe Generatioun 1/2/3

- SAS2/SATA3 (bis zu 6 Gbps)

- XAUI

- RXAUI

Zäitpunkt vun der Verëffentlechung: 30. September 2024