Souwuel SoC (System on Chip) wéi och SiP (System in Package) si wichteg Meilesteen an der Entwécklung vu modernen integréierte Schaltungen, déi d'Miniaturiséierung, d'Effizienz an d'Integratioun vun elektronesche Systemer erméiglechen.

1. Definitiounen a Grondkonzepter vu SoC an SiP

SoC (System on Chip) - Integratioun vum ganze System an engem eenzege Chip

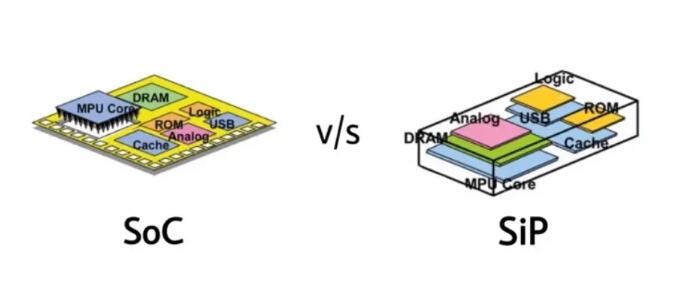

E SoC ass wéi e Wolkenkratzer, wou all funktionell Moduler an deeselwechte physesche Chip entworf an integréiert sinn. D'Grondidee vum SoC ass et, all Kärkomponente vun engem elektronesche System, dorënner de Prozessor (CPU), de Speicher, d'Kommunikatiounsmoduler, d'Analogschaltungen, d'Sensorinterfaces an déi verschidden aner funktionell Moduler, op engem eenzege Chip z'integréieren. D'Virdeeler vum SoC leien an sengem héije Grad vun Integratioun a senger klenger Gréisst, wat bedeitend Virdeeler a punkto Leeschtung, Energieverbrauch an Dimensiounen bréngt, wat en besonnesch gëeegent mécht fir héich performant, energieempfindlech Produkter. D'Prozessoren an Apple Smartphones si Beispiller vu SoC-Chips.

Zum Beispill ass e SoC wéi e "Supergebai" an enger Stad, wou all Funktiounen dran entworf sinn, a verschidde funktionell Moduler wéi verschidde Stäck sinn: e puer sinn Büroberäicher (Prozessoren), e puer sinn Ënnerhalungsberäicher (Speicher), an e puer sinn Kommunikatiounsnetzwierker (Kommunikatiounsinterfaces), all konzentréiert am selwechte Gebai (Chip). Dëst erlaabt dem ganze System op engem eenzege Siliziumchip ze funktionéieren, wat eng méi héich Effizienz a Leeschtung erreecht.

SiP (System in Package) - Kombinatioun vu verschiddene Chips

Den Usaz vun der SiP-Technologie ass anescht. Et ass éischter wéi wann ee verschidde Chips mat verschiddene Funktiounen an der selwechter physescher Verpackung verpackt. Et konzentréiert sech op d'Kombinatioun vu verschiddene funktionelle Chips duerch Verpackungstechnologie anstatt se an engem eenzege Chip wéi SoC z'integréieren. SiP erlaabt et, verschidde Chips (Prozessoren, Speicher, RF-Chips, asw.) niewenteneen ze verpacken oder am selwechte Modul ze stapelen, wouduerch eng Léisung op Systemniveau entsteet.

De Konzept vu SiP kann een mam Zesummebau vun enger Werkzeugkëscht vergläichen. D'Werkzeugkëscht kann verschidden Tools enthalen, wéi Schrauber, Hämmer a Buerer. Och wann et sech ëm onofhängeg Tools handelt, sinn se all an enger Këscht vereenegt fir eng bequem Benotzung. De Virdeel vun dësem Usaz ass, datt all Tool separat entwéckelt a produzéiert ka ginn, an datt se no Bedarf an e Systempaket "zesummegesat" kënne ginn, wat Flexibilitéit a Geschwindegkeet bitt.

2. Technesch Charakteristiken an Ënnerscheeder tëscht SoC an SiP

Ënnerscheeder an der Integratiounsmethod:

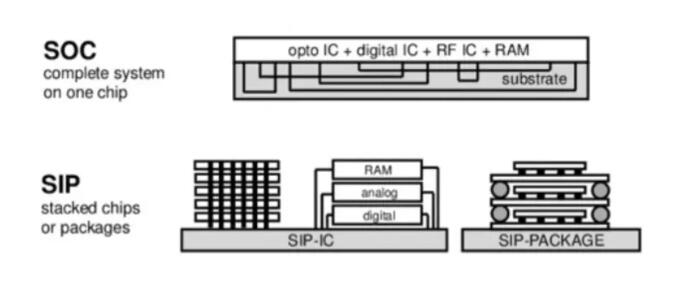

SoC: Verschidde funktionell Moduler (wéi CPU, Speicher, I/O, etc.) sinn direkt op dem selwechte Siliziumchip entworf. All Moduler deelen deeselwechten ënnerierdesche Prozess an Designlogik a bilden en integréiert System.

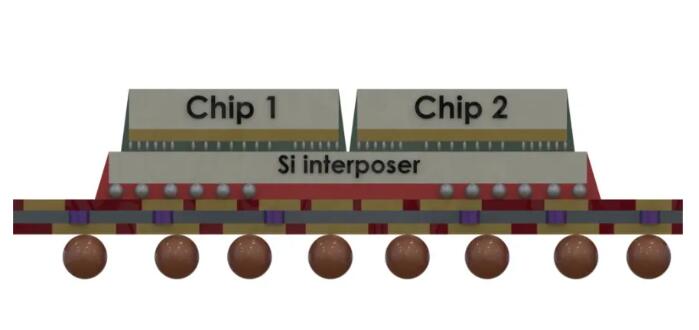

SiP: Verschidde funktionell Chips kënnen mat verschiddene Prozesser hiergestallt ginn an dann an engem eenzege Verpackungsmodul mat Hëllef vun 3D-Verpackungstechnologie kombinéiert ginn, fir e physikalescht System ze bilden.

Designkomplexitéit a Flexibilitéit:

SoC: Well all Moduler op engem eenzege Chip integréiert sinn, ass d'Designkomplexitéit ganz héich, besonnesch fir den kollaborativen Design vu verschiddene Moduler wéi digital, analog, RF a Speicher. Dëst erfuerdert vun Ingenieuren déifgräifend Cross-Domain-Designfäegkeeten. Ausserdeem, wann et e Designproblem mat engem Modul am SoC gëtt, muss de ganze Chip eventuell nei entworf ginn, wat bedeitend Risiken duerstellt.

SiP: Am Géigesaz dozou bitt SiP eng méi grouss Designflexibilitéit. Verschidde funktionell Moduler kënnen separat entworf a verifizéiert ginn, ier se an e System integréiert ginn. Wann e Problem mat engem Modul optrieden, muss nëmmen dee Modul ersat ginn, wouduerch déi aner Deeler net beaflosst ginn. Dëst erméiglecht och méi séier Entwécklungsgeschwindegkeeten a méi niddreg Risiken am Verglach mat SoC.

Prozesskompatibilitéit an Erausfuerderungen:

SoC: D'Integratioun vu verschiddene Funktiounen, wéi digital, analog an HF, op engem eenzege Chip, stellt bedeitend Erausfuerderungen an der Prozesskompatibilitéit duer. Verschidde funktionell Moduler erfuerderen ënnerschiddlech Produktiounsprozesser; zum Beispill brauchen digital Schaltunge séier Prozesser mat geréngem Energieverbrauch, während analog Schaltunge méi präzis Spannungssteierung erfuerderen. Et ass extrem schwéier, Kompatibilitéit tëscht dësen ënnerschiddleche Prozesser op deem selwechte Chip z'erreechen.

SiP: Duerch d'Verpackungstechnologie kann SiP Chips integréieren, déi mat verschiddene Prozesser hiergestallt ginn, an doduerch d'Prozesskompatibilitéitsproblemer léisen, déi mat der SoC-Technologie konfrontéiert sinn. SiP erlaabt et, datt verschidde heterogen Chips an der selwechter Verpackung zesumme schaffen, awer d'Prezisiounsufuerderunge fir d'Verpackungstechnologie si héich.

Fuerschungs- an Entwécklungszyklus a Käschten:

SoC: Well e SoC verlaangt, datt all Moduler vun Null un entworf a verifizéiert ginn, ass den Designzyklus méi laang. All Modul muss engem rigoréisen Design, Verifizéierung an Tester ënnerworf ginn, an de gesamten Entwécklungsprozess kann e puer Joer daueren, wat zu héije Käschte féiert. Wéinst der Masseproduktioun sinn d'Eenheetskäschten awer méi niddreg wéinst der héijer Integratioun.

SiP: De Fuerschungs- an Entwécklungszyklus ass méi kuerz fir SiP. Well SiP direkt existent, verifizéiert funktionell Chips fir d'Verpakung benotzt, reduzéiert et d'Zäit, déi fir d'Nei-Gestaltung vu Moduler gebraucht gëtt. Dëst erméiglecht méi séier Produktlancéierungen a senkt d'Fuerschungs- an Entwécklungskäschten däitlech.

Systemleistung a Gréisst:

SoC: Well all Moduler um selwechte Chip sinn, ginn d'Kommunikatiounsverzögerungen, d'Energieverloschter an d'Signalstéierungen miniméiert, wat dem SoC en onvergläichleche Virdeel a punkto Leeschtung a Stroumverbrauch gëtt. Seng Gréisst ass minimal, wat en besonnesch gëeegent mécht fir Uwendungen mat héijer Leeschtung a Stroumufuerderungen, wéi Smartphones a Bildveraarbechtungschips.

SiP: Och wann den Integratiounsniveau vu SiP net sou héich ass wéi dee vun engem SoC, kann et trotzdem verschidde Chips kompakt zesummepacken mat Hëllef vun der Multilayer-Verpackungstechnologie, wat zu enger méi klenger Gréisst am Verglach mat traditionelle Multichip-Léisunge féiert. Well d'Moduler kierperlech verpackt sinn anstatt um selwechte Siliziumchip integréiert ze sinn, kann et, och wann d'Performance net mat där vun engem SoC iwwereneestëmmt, trotzdem d'Bedierfnesser vun de meeschte Uwendungen erfëllen.

3. Applikatiounsszenarie fir SoC an SiP

Applikatiounsszenarien fir SoC:

E SoC ass typescherweis gëeegent fir Beräicher mat héijen Ufuerderungen u Gréisst, Energieverbrauch a Leeschtung. Zum Beispill:

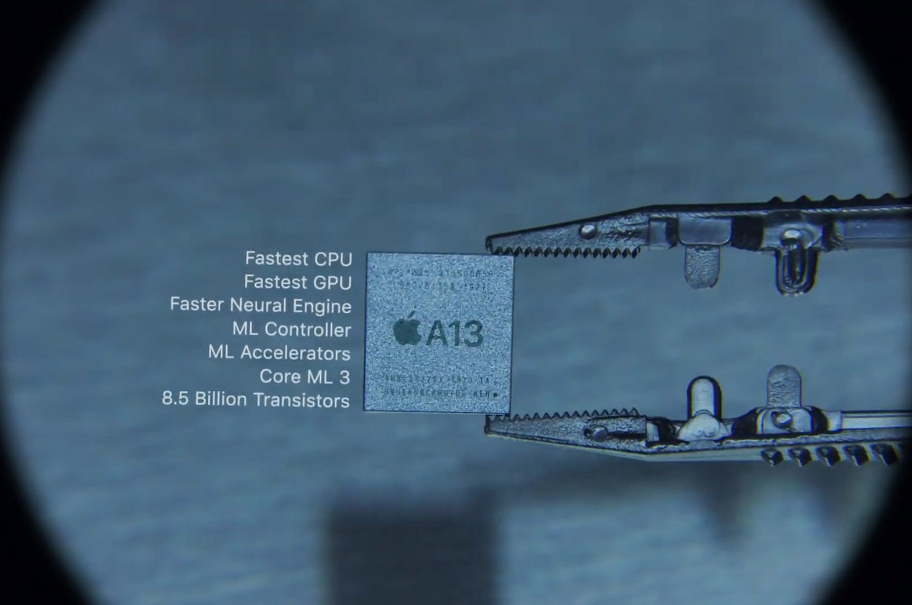

Smartphones: D'Prozessoren a Smartphones (wéi Apple seng A-Serie Chips oder Qualcomm säi Snapdragon) si meeschtens héich integréiert SoCs, déi CPU, GPU, KI-Veraarbechtungseenheeten, Kommunikatiounsmoduler, etc. enthalen, a souwuel eng staark Leeschtung wéi och e niddrege Stroumverbrauch erfuerderen.

Bildveraarbechtung: An digitale Kameraen an Dronen erfuerderen Bildveraarbechtungseenheeten dacks staark parallel Veraarbechtungsméiglechkeeten a geréng Latenz, wat SoC effektiv erreeche kann.

Héichleistungs-Agebettete Systemer: SoC ass besonnesch gëeegent fir kleng Apparater mat strengen Energieeffizienzufuerderungen, wéi IoT-Apparater a Wearables.

Applikatiounsszenarien fir SiP:

SiP huet eng méi breet Palette vun Uwendungsszenarien, gëeegent fir Beräicher, déi eng séier Entwécklung a multifunktionell Integratioun erfuerderen, wéi zum Beispill:

Kommunikatiounsausrüstung: Fir Basisstatiounen, Routeren, etc. kann SiP verschidde RF- an digital Signalprozessoren integréieren, wat de Produktentwécklungszyklus beschleunegt.

Konsumentelektronik: Fir Produkter wéi Smartwatches a Bluetooth-Headsets, déi séier Upgrade-Zyklen hunn, erlaabt d'SiP-Technologie méi séier Starte vun neie Featureprodukter.

Automobilelektronik: Kontrollmoduler a Radarsystemer an Automobilsystemer kënnen d'SiP-Technologie benotzen, fir verschidde funktionell Moduler séier z'integréieren.

4. Zukünfteg Entwécklungstrends vu SoC a SiP

Trends an der SoC-Entwécklung:

SoC wäert sech weider a Richtung vun enger méi héijer Integratioun an heterogener Integratioun entwéckelen, wat potenziell eng méi grouss Integratioun vun KI-Prozessoren, 5G-Kommunikatiounsmoduler an aner Funktiounen mat sech bréngt, wat d'weider Evolutioun vun intelligenten Apparater fördert.

Trends an der SiP-Entwécklung:

SiP wäert sech ëmmer méi op fortgeschratt Verpackungstechnologien, wéi z. B. 2,5D- an 3D-Verpackungsfortschrëtter, verloossen, fir Chips mat verschiddene Prozesser a Funktiounen enk zesummen ze verpacken, fir de séier verännerleche Maartufuerderungen gerecht ze ginn.

5. Schlussfolgerung

E SoC ass éischter wéi e multifunktionelle Superwolkekratzer ze bauen, wou all funktionell Moduler an engem Design konzentréiert ginn, deen fir Uwendungen mat extrem héijen Ufuerderungen u Leeschtung, Gréisst a Stroumverbrauch gëeegent ass. SiP ass dogéint wéi d'"Verpakung" vu verschiddene funktionelle Chips an engem System, wou de Fokus méi op Flexibilitéit a séier Entwécklung läit, besonnesch gëeegent fir Konsumentelektronik, déi séier Updates erfuerdert. Béid hunn hir Stäerkten: De SoC betount optimal Systemleistung an Gréisstoptimiséierung, während de SiP d'Systemflexibilitéit an d'Optimiséierung vum Entwécklungszyklus ervirhieft.

Zäitpunkt vun der Verëffentlechung: 28. Oktober 2024